10G TCP/UDP/IP Cores

Enter a new era of unmatched speed and efficiency for HFT and HPC.

Maximize speed and minimize latency with our 10G TCP/UDP/IP to stay ahead of the curve

High-performance TCP and UDP IP offload engine cores offer a reliable, ultra-low-latency solution for financial and network applications. They address the data center industry’s growing need for throughput and hardware acceleration and provide network protocol offload for applications such as financial data processing, reprogrammable Smart NICs, and high-performance computing.

Cutting-edge 10G TCP/UDP/IP Core for Next-Gen Trading

Unmatched Latency Performance

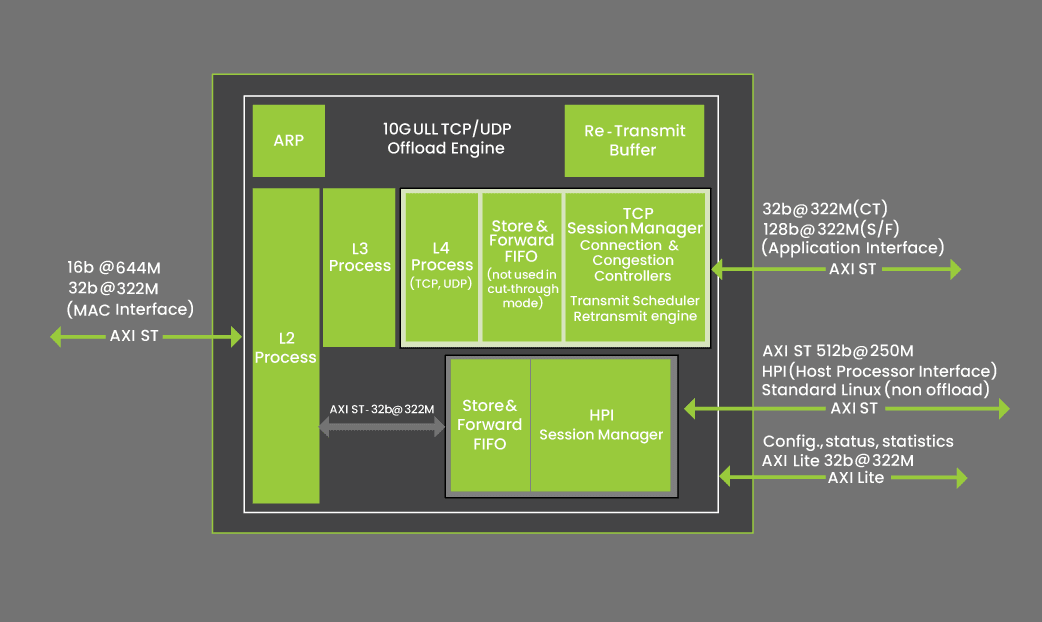

Best in-class latency and throughput performances with a full RTL implementation supporting layers 2, 3, 4 (ARP, IPv4, ICMP, TCP, UDP).

A complete range of IP Cores to support your needs

Three FPGA IP core versions are available through standard licensing options, including TCP/IP Offload Engine (ToE), UDP/IP Offload Engine, and a version supporting both TCP/IP and UDP/IP protocols offload.

Easy integration with complementary IP Cores

Easily integrated with innovative technologies such as our ULL Ethernet MAC PCS and PCIe DMA controllers, these cores radically change the way we think about speed and efficiency.

Experience seamless network connectivity with the latest FPGA-enabled network.

ULL 10 Gigabit TCP/UDP IP

Tx Processing Latency

6,2ns* TX

* Cut-through mode on AMD/Xilinx x3522pv platform

Our scalable frameworks evolve with your trading strategies, ensuring long-term performance and viability.

ULL 10 Gigabit TCP/UDP IP

Rx Processing Latency

6,2ns* RX

* Cut-through mode on AMD/Xilinx x3522pv platform

Pushing the boundaries of ultra-low latency and efficiency with Orthogone's 10G TCP/UDP IP Core

Experience seamless network connectivity with the latest FPGA-enabled network protocol stacks. Learn more about the specifications of our 10G TCP/UDP IP Core to boost your financial trading network.

Boost the performance of your applications with

our ULL 10G TCP/UDP/IP designed for FPGA

Our ULL 10G TCP/UDP/IP Core includes a rich standard and advanced features that make them ideal for various applications.

General Features

Layer 2 through Layer 4 solution

- ARP, IPv4, and TCP/UDP

- TCP/UDP session management

- Configurable number of connections, up to 64 per endpoint

- Server-side or client-side support, per connection

MAC Side Interface

- 16b AXI-4 @644MHz

- 32b AXI-4 @322MHz

Operating Mode

Store/Forward or Cut-Through Mode

On-Chip Applications

- 32b AXI-4 @322MHz (Cut-Through Mode)

- 128b AXI-4 @322MHz (Store & Forward Mode)

Redefine network performance with the

power of FPGA-enabled connectivity

Conceived primarily for high-frequency trading (HFT) applications, our 10G TCP/UDP IP Core is also designed for ultra-low latency networking applications for innovative industries that need the best performance.

High Performance Computing (HPC)

Networking

Storage

Security

Our ecosystem of technological partners

Here are the answers to some frequently asked questions:

We would be happy to develop FPGA solutions that combine our IP cores with modules specifically designed for your applications. This allows us to be very competitive since we have a detailed knowledge of all our IP cores as well as many blocks readily available to develop your solutions. Depending on your requirements, it is also possible for us to provide you with a complete design package allowing you to take ownership of the developed solution. We can also provide technical support and maintenance to give you peace of mind if you want us to make changes or add new features as your product evolves.

Ultra-low gate count & resources and ultra-low latency performances are the key differentiators. Our products also have excellent timing margin and a rich set of standard and advanced features. They are based on a unified architecture where all rates and options are supported using a unique Verilog source code and UVM environment.

All our IP cores are extensively verified in simulations using a Universal Verification Environment (UVM) methodology with a full suite of tests that ensures interoperability with the IEEE 802.3 standard. The products are also ported on FPGA platforms to test performances and verify interoperability with standard network testing appliance equipment.