Bring your trading strategies to the next level with our 10G Ethernet MAC/PCS IP Core

The ULL 10G Ethernet MAC/PCS is the industry leading solution for latency critical Ethernet applications.

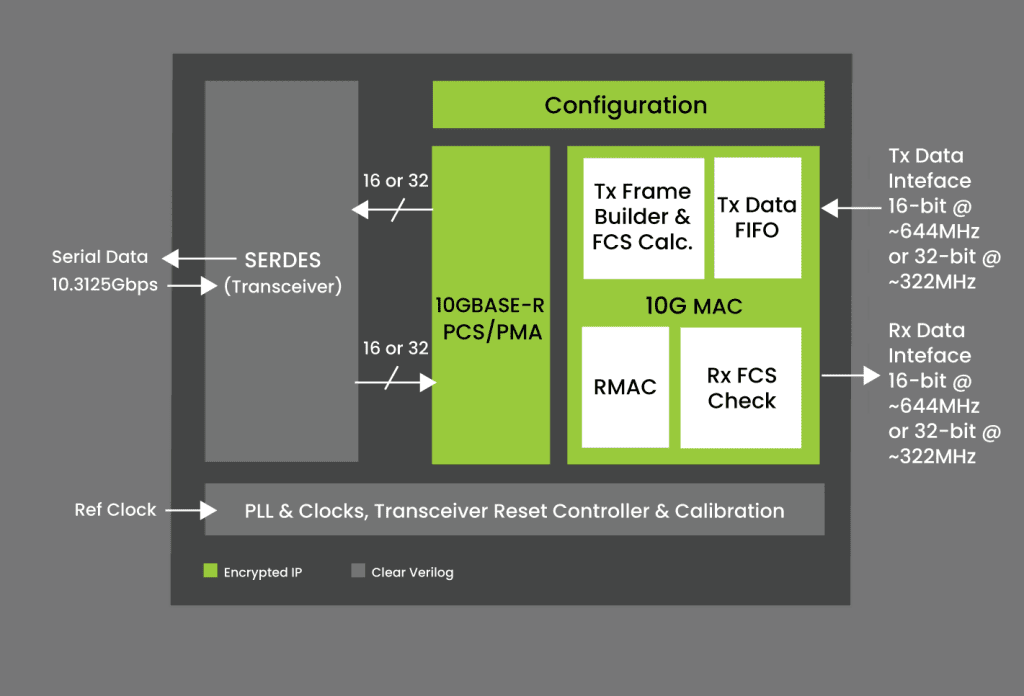

The core is designed using advanced design techniques leading to unmatched ultra-low gate count utilization and amazing latency performances. The 10G IP core support both 16b (644MHz) and 32b (322MHz) modes, and can support full wire line speed with a 64-byte packet length. It also supports back-to-back or mixed length traffic with no dropped packets.

Unlock lightning-fast trades by boosting your system performance

High speed, flexibility & scalability

Gain exceptional performance for latency-critical Ethernet applications. The 10G Ethernet MAC/PCS IP core is designed using advanced techniques, resulting in outstanding gate count utilization and latency performance.

Hardware Acceleration & Reliability

Unlock the potential of high-performance and seamless network connectivity by addressing the growing need for throughput and hardware acceleration in the data center industry.

Time-to-market optimized

Our 10G Ethernet MAC/PCS IP Core significantly reduces time-to-market and provide a fast and reliable solution for financial and networking applications. This results in unmatched and exceptional latency performance.

High-Level Block Diagram

Get first to the finish line with our Ultra-Low Latency 10G Ethernet for high-frequency trading (HFT) strategies

ULL 10 Gigabit Ethernet MAC/PCS

17,1ns*

Wire to Wire Round-Trip Latency 16b(GTY), 16b(AXI-4)

* Latency: GTY + MAC/PCS (Measured from TxSoP to RxSoF using serial loopback)

Our scalable frameworks evolve with your trading strategies, ensuring long-term performance and viability.

ULL 10 Gigabit Ethernet MAC/PCS

34,1ns*

Wire to Wire Round-Trip Latency 16b(GTY), 32b(AXI-4)

* Latency: GTY + MAC/PCS + CDC (Measured from TxSoP to RxSoP using serial loopback)

Unleash the full power of Orthogone's 10G Ethernet MAC/PCS IP Core

Learn more about the specifications of our 10G Ethernet IP Core to boost your financial trading network

Boost your trading network performance with our ULL 10G Ethernet MAC/PCS designed for FPGA

Our ULL 10G Ethernet MAC/PCS solution is designed to deliver measurable ROI by reducing trade execution times and enhancing system efficiency.

General Features

User Logic Interface

AXI-4 Stream 16b @ ~644MHz

or AXI-4 Stream 32b @ ~322MHz

SERDES Interface

16b @ ~644MHz

or 32b @ ~322MHz

Early Signaling

Early SoP Indication (Tx)

and Early SoF Detection (Rx)

MAC Features

FCS Processing

Tx Frame Check Sequence (FCS) computation and insertion

Rx FCS Error detection

Timing Margin

High Timing Margin @ 322 MHz

Adequate Timing Margin @ 644 MHz

Compatibility

Fully compatible with Orthogone 10G TCP/UDP IP core

PCS Features

Supports 10GBASE-R PHY based on 64B/66B encoding and scrambling

Supports block synchronization

Unlock the power of FPGA for unmatched speed and reliability

Designed primarily for high-frequency trading (HFT), our 10G Ethernet MAC/PCS IP Core also delivers ultra-low latency network for cutting-edge applications demanding top-tier performance.

SmartNIC

High-Frequency Trading

Low-Latency Switches

Our ecosystem of technological partners

Here are the answers to some frequently asked questions:

We would be happy to develop FPGA solutions that combine our IP cores with modules specifically designed for your applications. This allows us to be very competitive since we have a detailed knowledge of all our IP cores as well as many blocks readily available to develop your solutions. Depending on your requirements, it is also possible for us to provide you with a complete design package allowing you to take ownership of the developed solution. We can also provide technical support and maintenance to give you peace of mind if you want us to make changes or add new features as your product evolves.

Ultra-low gate count & resources and ultra-low latency performances are the key differentiators. Our products also have excellent timing margin and a rich set of standard and advanced features. They are based on a unified architecture where all rates and options are supported using a unique Verilog source code and UVM environment.

All our IP cores are extensively verified in simulations using a Universal Verification Environment (UVM) methodology with a full suite of tests that ensures interoperability with the IEEE 802.3 standard. The products are also ported on FPGA platforms to test performances and verify interoperability with standard network testing appliance equipment.